Dataflow Model

A dataflow model is a description of a circuit which can use logical expressions with continuous assignments. Modelling at such a abstraction level is to be contrasted with the higher level behavioural modelling and the lower level structural modelling.

Example

Consider a half adder which adds bits A and B giving the sum S and carry C.

The truth table below gives the specification:

A | B | S | C |

|---|---|---|---|

0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 |

1 | 0 | 1 | 0 |

1 | 1 | 0 | 1 |

The simplified equations for the half adder are:

S = A xor BC = A and B

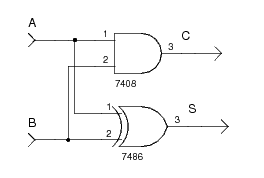

In schematic form this is:

Below is a Verilog dataflow model for the half adder. Notice how it contains the simplified logical equations given above.

module half_adder(S, C, A, B);

output S;

output C;

input A;

input B;

assign S = A ^ B;

assign C = A & B;

endmodule

References

Mano, M. Morris, and Kime, Charles R. Logic and Computer Design Fundamentals. 2nd Edition. Prentice Hall, 2000.

Kleitz, W. Digital Microprocessor Fundamentals. 3rd Edition. Prentice Hall, 2000.